准确分析脉冲抗扰度—分析电子系统抗干扰路径时的物理问题

1、引言

今天,在最先进的电子电路中找到故障正变得越来越难。除了更加复杂(并且因此一些高得多的潜在故障源),小机械尺寸让开发人员越来越难查明故障。下面是北京海洋兴业科技股份有限公司进行测量的例子。

2、任务

一个新的干扰发生器抗扰度试验的控制单元是检查的对象。该电路板包括液晶显示器(+控制器)、μC(142引脚TQFP)、FPGA(100引脚TQFP)、接口模块、无源器件(如SMD0603)和各种控制元件(旋转编码器、按钮、开关)。此外,在电路板承载的USB插座,连接器用于将随后由发生器和电源输入来产生的电压。由于成本原因,电路板被设计成具有200微米特征尺寸的双层系统。没有连续的GND层。该总线/线放在两个层次。控制单元向发生器单元的接近导致高抗干扰要求。

根据DINEN61000-4-2,功能故障发生在第一次ESD测试中。干扰脉冲(接触放电)连接到电路板的接地系统后,微控制器出现故障,通过跳动信号故障和定格显示变得明显。这种故障发生在不同的电压(2.4kV-4kV)取决于静电枪的位置(连接点和角)。显然抗扰水平必须提高。

3、耦合机制

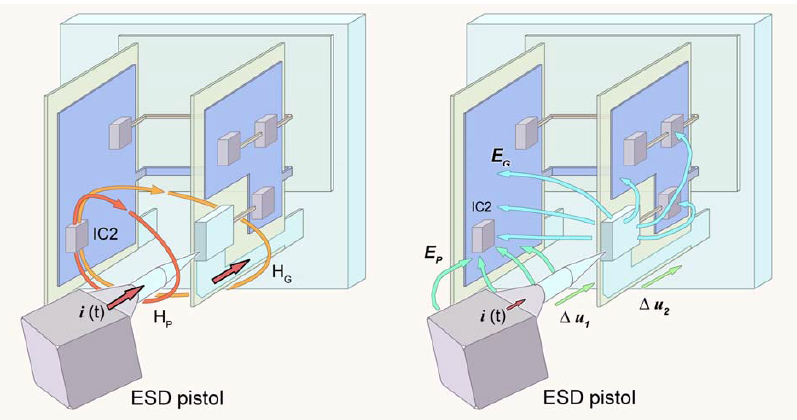

如图1所示是两种电电位耦合机制,通过该干扰可能到达电路板重要区域:磁耦合和电耦合。

当使用ESD静电枪耦合扰动到模块时,区别在:

磁耦合期间,干扰电流流过电路板,并产生磁性,这反过来又可能在导体回路感应电压。这些电压可能导致两种不同类型的问题:感应电压既可以视为由该电路的输入逻辑信号,又可视为它驱动扰动电流,这会在控制电路的其它部分引起问题。

图1在IC上电场和磁场的效果

电耦合也可引起干扰。电场电容耦合到电路板的线路网络或组件。所得位移电流可能反过来以两种不同的方式影响系统:位移电流可能导致在电阻器上的电压降(反抗VSS或VDD),这再次被认为是一个逻辑信号,或在类似于磁耦合引起的电路其他部分感应电压。

干扰必须被施加到选择的各个线路(例如,在总线系统)和/或它们的通孔或单个IC引脚以查明易敏感模块组件。在微米范围内的电路和特征尺寸的一体化的上述高层导致对干扰源的机械分辨率越来越高的要求。

更多详细资料,请下载:![]() 准确分析脉冲抗扰度中文版本.pdf

准确分析脉冲抗扰度中文版本.pdf

版权声明:本资料属于北京海洋兴业科技股份有限公司所有,如需转载,请注明出处!